# CARNEGIE MELLON UNIVERSITY

RVMDES: A Tool for Efficient Design of Complete, High Speed, Image Processing Machines

A DISSERTATION

SUBMITTED TO THE GRADUATE SCHOOL

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

for the degree

DOCTOR OF PHILOSOPHY

in

ELECTRICAL AND COMPUTER ENGINEERING

by

RICHARD MADISON

Pittsburgh, Pennsylvania July, 1997

|   |  | € <u>*</u> **<br>6 - <sub>€</sub> • *• |

|---|--|----------------------------------------|

|   |  |                                        |

|   |  |                                        |

| · |  |                                        |

|   |  |                                        |

|   |  |                                        |

|   |  |                                        |

|   |  |                                        |

## **Abstract**

The parts inspection industry requires image processing machines operating at speeds unattainable by microprocessor systems. Parallel processors can provide higher speeds, but often the speeds required can only be achieved using custom hardware. Unfortunately, building machines fi-om custom hardware involves long and expensive design cycles. However, this time and expense can be dramatically reduced by building machines fiom reconfigurable vision systems, consisting of hardware modules that can be connected by plugging them into special motherboards. Using this modular hardware reduces design cycle time **and** cost, by practically eliminating **the** hardware design and fabrication stages, but writing and testing programs to run on modular hardware networks is still time consuming, and requires detailed knowledge of the hardware.

This thesis presents the concepts behind and implementation of a new design environment, in which users can quickly design high speed image processing machines fi-om a set of modular hardware blocks. Like design tools for multiprocessor systems, this environment allows a user to write and test block diagram algorithms, partition them onto hardware networks, simulate the timing for each module, and generate executables for any programmable hardware. Unlike previous tools, the new environment models custom hardware as well as processors, assists in optimizing processor software, and includes tools to design all aspects of an image processing machine, such as hardware configuration and user interface. The environment, called RVMDES, will be basis for a real tool to design reconfigurable vision machines from the modular hardware developed by the Egipt group at CMU.

# **Contents**

| I.        | Introduction                      | P.1   |

|-----------|-----------------------------------|-------|

| n.        | Algorithm Design in RVMDES        | p.8   |

| III.      | Streamlined Hardware Design Cycle | p.23  |

| IV.       | Software Optimization             | p.40  |

| v.        | Automatic Code Generation         | p.56  |

| VI.       | Configuring RVM Hardware          | p.77  |

| VII.      | Interfacing with an RVM           | p.94  |

| VIII.     | A Complete Example                | p.101 |

| IX.       | Conclusions                       | p.108 |

| Appendix. | lix. Function Library             | p.112 |

| ••        | References                        | p.118 |

# Acknowledgments

I would like to thank Barrett Trask for implementing and testing the RVM configuration search algorithm, Bill Ross for implementing the software simulator and primitive editor, Dr. Takeo Kanade for the idea of applying the work to the Egipt RVS, and the Raven Lab for providing the equipment on which the research was done.

## I. Introduction

## A. High Speed Image Processing Machines

Industrial image processing applications require higher frame rates than a single microprocessor or DSP can provide. For example, Kirin Techno Systems' ink jet printing inspection system must process relatively small images (256x160) at 30 frames per setond, about 20 times faster than the inspection algorithm runs on a standard DSP (Texas Instruments C40, 50 MHz), programmed by an expert. Other applications must be even faster, completely processing a fiame in a fraction of the interval before the next frame is captured. Such low latency systems are necessary when an inspection station's camera and effector must be mounted close together, because an inspected item travelling on a conveyer belt reaches the effector before the next item reaches the camera.

The reason that microprocessors and **DSPs** cannot provide these speeds is that they are serial machines. When implementing simple image processing functions, they repeat the same instructions for every pixel in **an** image. Images contain a huge number of pixels (even a 256x256 image has over **65** thousand pixels), so processor implementations of functions that process one at a time are bound to be slow. Complex hnctions that use fewer pixels often perform complicated math, again one instruction at a time, and so are also slow. While processor speed increases every year, image processing algorithms become increasingly subtle and sophisticated to match, so algorithm speeds do not increase. Thus, to achieve high image processing speeds, industrial designers have turned from single processors to custom hardware, multiprocessing and reconfigurable vision systems.

Custom hardware, such as FPGA or ASIC chips, can perform simple image processing tasks in a fiaction of the time required by a processor, and at lower costs. Unlike general purpose processors, custom hardware only includes the components it needs for its processing task. When an image processing task does not require much hardware, a processor sized chip can hold several copies of the hardware, to process several pixels at once. Alternately, it can hold additional components such that each component is only used once while processing a pixel, and processing can be pipelined. The pipeline can include I/O operations, eliminating the need for memory to buffer the input and output, further decreasing space requirements. If adding components cannot increase processing **speed**, for instance if speed is limited by I/O bandwidth, the reduced hardware can be implemented on a smaller, less expensive chip. For these reasons, custom hardware provides an attractive replacement for processors.

Custom hardware is made less attractive however, by the difficulties in designing it. There exist software tools to help program individual chips, but they do not allow users to design networks of chips, or to route connections between chips. The user can only determine interaction between chips by staring at waveforms generated by the chip simulators, to see whether they are all compatible. Further, the designer must spend time and money building the chips into a printed circuit board, having the board built, and testing whether his estimates of the interaction were correct. **As** a result, the majority of the design time is

spent on tasks not related to the algorithm. Worse still, a small change to the algorithm can require a whole new round of hand-calculated simulation of hardware interactions, and a complete redesign of the circuit board. As a final insult to hardware designers, the tools that would simplify the design process are unlikely to be created, because there are too many types of hardware, with too many communication schemes and too many packages to cover them all in one design program.

An alternative architecture for fast image processing is the multiprocessor network. In such a system, an image processing task is split over several processors, each performing a hotion of the work in a fraction of the time required by a single processor. Processors are as fast as custom hardware when tasks require a large number of components, and designed to implement functions of any complexity. Thus a system with arbitrary functionality could be built from a network of processors. Several companies provide the software tools necessary to quickly program such networks. Other companies produce processor modules that can be plugged together to quickly implement the networks.

While multiprocessor networks are thus flexible and easy to build, they are less attractive than custom hardware systems in many ways. Processor networks have higher latencies than custom hardware chips because they must transfer data between processors, which is slower than passing data within a single, custom hardware chip. Also, processors cannot pipeline their data processing and I/O stages, so they must increase their latency or frame time to transfer data. Further, it is simply not cost effective to use several processors to carry out simple operations that a single custom hardware chip could accomplish at the same speed.

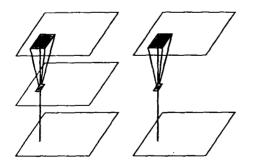

One way to provide the processing speed of custom hardware along with the ease of designing and building processor networks is to use a reconfigurable vision system (RVS). **An** RVS consists of a set of hardware modules with a common communication interface and physical characteristics, each containing one processor or custom hardware chip. The set of hardware chips is chosen to reflect the specialized needs of computer vision and image processing algorithms. **As** with multiprocessor systems, a designer can quickly plug RVS modules together to build **an** image processing machine. Because the set of chips involved is finite, it is also possible to build a software design tool that facilitates design of the entire machine. Finally, because the RVS modules include both processors and custom hardware, the user **can** build machines fiom **an** optimal mix of fast custom hardware and slower but more flexible processors.

# **B.** The Egipt RVS

The Egipt group at CMU has created a reconfigurable vision system. Because reconfigurable vision machines do not seem to be a current product or area of research, the Egipt RVS draws mainly on concepts fi-om current modular processor systems. It then adds to these ideas, by tailoring modules to handle large images, providing more ways to connect modules, and providing non-processor modules.

Current modular processor systems typically consist of modules, each containing a pro-

cessor, I/O buffers, memory and connectors, along with special motherboards hosting slots for the modules. The motherboards power the modules and provide traces that connect the I/O ports of the modules in its slots. Additional traces connect module I/O ports to connectors for ribbon cables that transfer data between multiple boards. Modules are often built around Texas Instruments **C40 DSPs**, which have six I/O ports. These systems' motherboards have three or four slots for modules, so that each module's six ports almost fully interconnect it with the other modules on a board, and with ribbon cable ports leading to and from other boards.

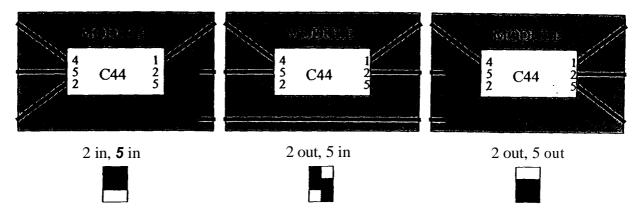

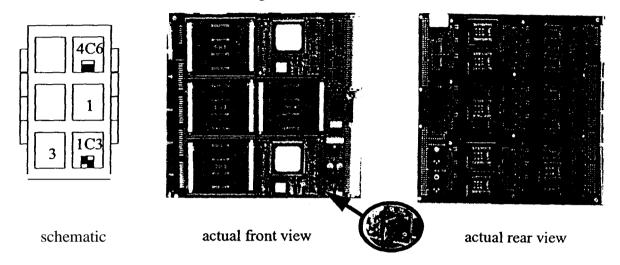

The Egipt RVS is based on the Texas Instruments C44 DSP, a smaller version of the C40. The C44 has a reduced number of communication ports, allowing less interconnection between modules, but it can be incorporated into a smaller module, so that six modules can fit on one motherboard. A single board can then hold several parallel processors along with an input broadcaster module and output collector module, with no intervening cables to slow down data transmission. In the most common modular processor motherboards, made by Hunt Engineering, cable transfers require double the time of on-board transfers, which can cause a bottleneck when transfemng large images. The higher number of modules per board will remove this bottleneck.

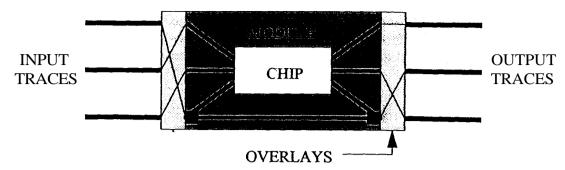

In addition to the new processor, the Egipt RVS modules contain more memory, faster I/O ports, and extra connector pins. The memory is double that of the most common Hunt Engineering C40 modules, to hold twice the number of intermediate images during processing. The faster I/O ports can send bursts of data at high speeds, to transfer images between modules in short periods of time. The extra connector pins provide new ways to communicate with the custom hardware that can be built into RVS modules in place of the C44. For instance, there are new lines to exchange signals with A/D and D/A modules through the motherboard, rather than over separately connected cables. There is also an extra pin for each communication port, to tell whether data or commands are being passed, in case hardware only has one port for both. More pins attach each module to a common bus, which allows most modules to communicate with each other, despite how their regular communication ports are connected.

The Egipt RVS motherboards also differ from their processor based predecessors, to handle custom hardware and the larger number of modules per board. Custom hardware modules cannot always remap which ports pass which data, so a fixed trace between two ports in two slots may not suitably connect hardware modules in those slots. To compensate, Egipt motherboards use special overlay cards that map the traces ending at each slot to the ports in that slot. This allows a single trace to properly connect two slots, no matter which ports are involved in the connection. In addition to port complications, RVS motherboards must compensate for the low connectivity between their modules. Each module has only three output ports, so traces can only connect it to 3 of the 5 other modules on the board. It cannot even use all of these if the module must communicate with another board or send parallel data streams to a hardware module with fixed port usage. To increase the number of connection options, overlay cards can short traces across slots instead of connecting them, creating new traces. A third complication to connectivity is that processor ports are typically bidirectional, but must be connected to either input or output traces, not

both. If a processor has fewer than six ports, some processor ports are assigned as inputs or outputs, while others are assigned a pair of connections. The designer must set jumpers on the module to determine which of the pair is actually used.

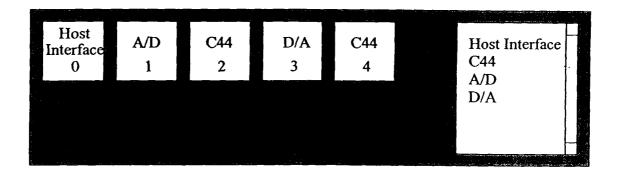

The remaining feature of the Egipt RVS is that it contains all of the hardware necessary to build a complete reconfigurable vision machine (RVM). It includes modules or plans for modules built around a C44 processor, fiame grabber, video display, data broadcaster, data merger, FPGA, convolver, and host interface. The host interface module communicates with the RVM operator on a PC and with the other hardware modules. It boots the and test the RVM, sends new parameters to the program running on it, and receives statistics output by the program. It talks to the hardware modules over a global bus, formed by connecting each motherboard's common bus using a VME bus. The host interface is necessary for many image processing applications, including inspection, where important parameters may vary with lighting conditions and need to be tuned by a human, and teleoperation, where the RVM is only semiautonomous.

The various new features of the Egipt RVS allow it to provide performance superior to the current, processor-only, modular vision systems. However, those same features complicate the design of the Egipt RVS. Therefore, effective design of RVMs using the Egipt RVS requires a software tool that supports both the features of a multiprocessor system, and the new features of the RVS.

## C. Toward a Design Tool

A design tool for the Egipt RVS must allow users to design the various aspects of a reconfigurable vision machine (RVM). First, it should let the user generate and simulate an algorithm with a minimum amount of work. The tool should also allow the user to choose hardware and partition the algorithm onto it, again with minimal work, then automatically generate the code or parameters each hardware module requires to execute its piece of the algorithm. Code should be optimized, automatically or with minimal user intervention, to take advantage of the structure of image processing functions. The tool should automatically configure hardware modules onto motherboards in a way that provides all necessary connections between modules. The tool should provide timing estimates for a design, and an easy way to identify and remedy timing bottlenecks. Finally, it should build a user interface, since it knows what data should be passed to and from the machine. Again, this should be automatic or require minimal help from the user. There is some existing work in some of these areas, but previous work addresses only a few of the requirements, and some of the requirements seem completely unexplored.

#### 1. Programming Environments

The requirement for an easy to use algorithm programming and simulation interface is well addressed by several visual programming environments, such **as** Khoros [1] and AVS [2]. These environments use block diagrams to represent algorithms, so that a user can quickly assemble an algorithm without writing low level code. The block diagram also serves as an interface for simulating the algorithm, allowing the user to quickly cycle between building and testing parts of **an** algorithm. Visual programming environments

will even convert a block diagram into C code or **an** executable, so that it can run outside the environment. Visual programming environments are excellent for generating code for a microprocessor machine, but lack most of the features needed to generate **high** speed vision machines. For instance, they do not include any concept of hardware beyond a single microprocessor, and do not optimize their code.

Design environments for modular multiprocessor networks take over where visual programming environments leave **off**, allowing the user to generate hardware and partition software onto it, all in terms of block diagrams. Some environments customized around the **C40** DSP [3][4] **also** simulate hardware, to provide the user with timing information, even modeling interactions between the multiple processors. From this, the user can identify bottlenecks and determine how to modify the design to compensate. Other environments that are not customized for a particular processor [5] cannot model timing, but can write code for several types of processors, allowing the user more flexibility in his design.

These design environments come closer to meeting the requirements for a design tool for the Egipt RVS, but they still do not solve several parts of the design problem. They only allow the user to design with and simulate processor modules. Their simulation is even of dubious value, since the Texas Instruments **C40** emulator they use does not account for cycles spent waiting for pipeline conflicts to clear, which can sometimes account for half of a **C40's** time. The environments are not affiliated with any particular modular hardware system, so they do not provide the user with a hardware configuration, check that designs can be implemented with a modular system, or generate an interface to the system. They also do not attempt to optimize code to account of the predictable structure of the image processing functions they implement.

#### 2. Optimizations for Image Processing Software

There **is** a reasonable amount of work on optimizing image processing programs, particularly for silicon compilers. Unfortunately, none of it looks at the high level optimizations available when the functionality **of** programs is restricted to image processing.

One line **a** research focuses on optimizing code or facilitating code writing, for image processing and other DSP applications. Some papers [6][7][8] consider how to optimize assembly code or tree representations of **equations** to be translated into optimal assembly code. Others recommend **generic** optimizations such **as** expanding function calls or constants in-line, or removing loop independent calculations **from** loops [9][10][11]. These optimizations **are** very low level and **can** be **performed** by optimizing compiler, used to compile C code from a visual programming environment. The Texas Instruments C40 compiler, typically used to compile code for C40 and **C44 DSPs**, handles these optimizations.

A second set of work [12][13][14] analyzes image processing functions to distill a set of primitive structures, finctions and functionals needed in **an** image processing programming language. A language with these primitives would allow a user to more explicitly represent his intentions in his code, making the code easier to write. Presumably, a compiler could also pattern match against the new primitives, recognizing opportunities to

optimize them that it could not have seen by looking at their translations. Unfortunately, the primitives are only useful for the proposed RVM design tool in a limited way. The block diagrams of Visual programming environments provide an easier way to write algorithms than the text based, image processing languages, and already include the recommended primitives. A specialized language could be used for function definitions, but if blocks represent image processing primitives, their definitions should not use other primitives, so using a language with these primitives avails nothing. What is useful about this research is the implication that image processing functions should be written in a format specifically designed to help a compiler recognize the special optimizations the apply to them.

A related set of work consists of the two languages Apply and Adapt [15]. These languages are based on the realization that many image processing functions apply some operator to each pixel or window in an image. A user writes programs by coding image processing function kernels and specifying the images they should be applied across. A compiler then decides the optimal way to split the processing over an array of parallel processors. The problem is that splitting a function over parallel processors is of limited value in an RVM, where low interprocessor connectivity makes fanning data out to a large array of processors a hardware intensive, high-latency operation. RVMs are better optimized by pipelining successive functions across several hardware modules. Thus, an RVM design tool should look for optimizations that take advantage of the relationship between functions partitioned onto each module, not try to split individual functions over parallel modules. Thus the actual optimizations made possible by Apply and Adapt are not directly useful for the RVM design tool. However, two languages further the notion that image processing functions should be coded in a format that leverages their special structure to help a compiler recognize opportunities for optimization. And they reveal that this special structure consists, at least in part, of a loop applying a function kernel to each pixel of an image.

#### 3. Missing Areas

The work mentioned above explores the areas of algorithm creation and testing, partitioning of an algorithm onto hardware, code generation, and to some extent software optimization. However, none of the work attempts to cover all of these areas. Further, none of them create actual hardware designs to implement hardware networks, apply high level optimizations to their software, generate **an** interface for their networks, or provide realistic timing estimates, especially for heterogeneous hardware.

#### D. RVMDES

This thesis presents the concepts behind and implementation of RVMDES, an integrated design environment allowing efficient design of complete, optimized, high speed image processing machines using Egipt RVS modules and motherboards. The environment is similar to multiprocessor network design environments, providing tools for algorithm design, simulation, partitioning, and code generation. However it adds tools for configuring RVM motherboards, simulating the timing of a heterogeneous hardware system, applying optimizations tailored to image processing programs, and creating programs to

interface with the RVM.

The chapters of the thesis explain the components of the tool. The thesis begins with an account of how RVMDES leverages the properties of image processing functions to facilitate the design of an algorithm and then the hardware to implement it. Next, it shows how RVMDES uses those same properties to automate or facilitate software optimization, code generation, hardware configuration and interface generation. Throughout, it follows the progress of an example application as each design step is applied. The thesis concludes with a complete example of using RVMDES to build as second application, and a discussion of the contribution of the work.

# 11. Algorithm Design in RVMDES

The first step in designing **an RVM** is to design the algorithm it will implement. This can involve a lot of design-and-test iterations, because design specifications often contain input-output pairs, not algorithm ideas. The design process thus involves inventing and coding a possible algorithm, then iteratively testing and modifying it until produces the proper set of outputs, or must be scrapped in favor of a completely different algorithm. This iteration can be time consuming, because modifications to the initial algorithm are often extensive, and may involve starting from scratch several times.

To reduce the time required to design an algorithm, RVMDES provides a user interface that **makes** each design step **as** efficient **as** possible. The interface represents algorithms **as** block diagrams, which are easy to build, simulate and modify. They are also easy to interpret, in case the user forgets what part of the algorithm does **as** he works on another part, or the algorithm must be reused later. **Also**, block diagrams provide an excellent structure around which to generate and optimize code, and to map algorithms onto hardware. Block diagrams do not provide the **full** flexibility cf text based languages, but they can be specifically designed to represent all of the structures needed in a limited domain like image processing. This chapter explains how RVMDES block diagrams can be used to describe image processing algorithms, and how the RVMDES software editor facilitates editing and simulation of block diagram algorithms.

## A. The RVMDES block diagram

The RVMDES block diagram representation provides blocks for the functions, inputs, outputs, and decision points in an image processing algorithm. All blocks are named for easy identification, and are marked with ports to represent the inputs they require and the outputs they produce. Connections between these ports show how data **flows** through the blocks. Input ports each read data fiom one source and thus end one connection, but output ports can each begin multiple connections, providing their data to several blocks. A diagram built fiom these blocks shows one *frame* of an algorithm, in which one set of inputs is processed to produce one corresponding set of outputs.

Two syntax rules constrain how the blocks are connected, to ensure that RVMDES will be able to simulate an algorithm and turn it into an RVM. The first rule is that a block's input ports must all connect to other blocks' output ports. A block cannot execute until valid data is available to each of its input ports. This data is read through connections to other blocks, and is made valid when those blocks execute. If an input port is unconnected, valid data is never provided, and the block can never run. Inclusion of an unusable module either represents a user oversight or an unnecessary obstacle to program readability, so RVMDES disallows it. The second rule is that an output port of a block may not begin a chain of connections and function blocks that ends as an input to the original block, forming a loop. Such a loop would present a paradox wherein a block cannot execute until its inputs are valid, but it must execute to start the chain of blocks that produces those inputs. A meaningful order of execution cannot be constructed for these chains, so RVMDES disallows them. If an algorithm requires a loop, a legal one can be built with the help of

branch and join modules, as explained later.

The block diagram representation was chosen for RVMDES because it makes steps of software design efficient. Block diagrams are easy to program with, because they allow the user **to** think directly in terms of the algorithm components and data flow, not in terms of the text and programming language idioms that implement it. This saves the user time not only because he does not have to write functions definitions, but also because he does not have to debug them or switch between thinking about the algorithm and thinking about individual functions. Block diagrams are also easy to understand, because the set of functions and the flow of data between them are explicit, not embedded in text. This allows a new user to quickly understand and reuse existing code, and it allows a current user to keep track of what his algorithm is doing. Block diagrams provide a straightforward interface for simulation, allowing a user to step through the diagram, simulating each block. This simulation can be completely integrated into the block diagram editor, so that blocks can be replaced and re-simulated until they produce the desired results, rather than requiring a new simulation with every change to the algorithm. Finally, block diagrams are easily partitioned onto hardware, by assigning each block to a hardware module, and blocks are easy to associate with hardware and/or code that implements them.

## B. Block diagram blocks

RVMDES provides several types of blocks from which to build block diagrams. These blocks are not sufficient to implement some programming constructs, such as recursion, but are specifically chosen to be able to represent the constructs required for most image processing programs. This section explains the types of blocks provided by RVMDES, as summarized in table 1.

| Block Type | Purpose                                           |  |

|------------|---------------------------------------------------|--|

| Function   | Image processing task                             |  |

| Input      | Data read at beginning of frame                   |  |

| output     | Results written at end of frame                   |  |

| Constant   | Data already present at beginning of <b>frame</b> |  |

| Branch     | Decision point, allowing multiple execution paths |  |

| Join       | Merge point for multiple execution paths          |  |

| Wraparound | Way of holding data between frames                |  |

| Undefined  | Place holder for an unavailable function block    |  |

**Function** blocks are the heart of an algorithm, used to perform image processing tasks. RVMDES provides a library of image processing functions. When a user creates a function block, he must specify which library function it will represent. The definition of the

associated function tells RVMDES which executable the block will call during simulation and what code or custom hardware can implement the block in an RVM. The definition also specifies the number and meaning of the function block's input and output ports. As with all module types, RVMDES records and allows the user to change the name of a function block and data types of its output ports.

Input blocks represent data that is read at the start of a fi-ame, either from a file during simulation, or from a camera or other sensor in the RVM. Each block has one output port, from which other modules can read this data. RVMDES records the data type and dimensions of the data represented by each input block, so that the algorithm simulator and code generator know how much memory to allocate and fill. RVMDES also propagates the dimensions through the block's output connections to other modules. In general, the user must set the dimensions, although RVMDES provides the option to read the dimensions as inputs to the input block. This allows the user to equate the dimensions of two input blocks before those dimensions are known. Input and constant blocks must have their dimensions set, so that dimensions of data can be propagated through the program.

*Output* blocks are the simplest type, representing the endpoints of **an** algorithm. Each reads a single data item **from** its single input port, and writes it to a file in simulation, or to an output device such **as** a monitor in the real application.

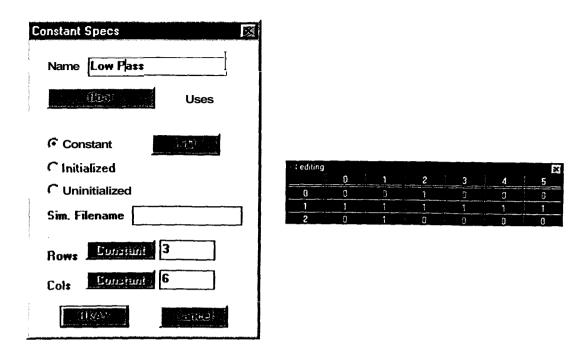

Constant blocks represent inputs to the algorithm that are not loaded at the beginning of each frame. Examples are convolution masks and parameters that evolve over several frames. Like input blocks, constant blocks have data type and dimension parameters to identify how much memory they require, can read their dimensions as inputs, and provide a single output port. Unlike input blocks, constant blocks come in three flavors -- initialized, uninitialized, and initializing. Initialized constant blocks contain user defined data. They are useful for small items like scalars, convolution masks and the initial values of evolving parameters. Uninitialized constant blocks have no initial values, and simply reserve memory. They are sufficient for accumulators that must be initialized each frame, such as Hough transform planes, and do not bloat executables with unneeded initialization values. Initializing constant blocks read their values at run time, before the first frame is processed, and can be reset by the RVM operator between frames. This is useful for parameters that cannot be determined before the RVM runs, such as thresholds that vary with lighting conditions.

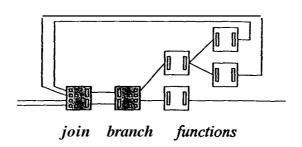

Branch blocks provide flow control for block diagram programs, allowing loops and other fancy control structures. To this end, each branch has a bundle of input ports, several identical bundles of output ports, and a test associated with each output bundle. These tests are equalities and inequalities like those found **in** 'if statements in C code, except the final test which always evaluates true. More complicated tests like those involving looping operations can be implemented by cascading branches. When executed, a branch block performs its tests in sequence, until one evaluates to true. It then passes its input data to the output bundle associated with the successful test. Because a block can only execute once its inputs have been calculated, only blocks attached to the successful bundle of output ports will be able to execute. The number of output bundles and number of ports

per bundles is variable, allowing the user to choose the number of conditional paths. Branch blocks must have all of their tests defined, and must have at least one input port and one output port, to insure that the branch can execute, and that execution will continue after it.

Join modules are the counterpart to branches, with several bundles of input ports funneling to one bundle of output ports. Once all inputs on a single bundle are valid, the join can be executed, passing the active bundle's data to its output ports. They are used in conjunction with branch blocks, the branch splitting execution over multiple paths, and the join recombining those paths. Like branch modules, they have a user-controlled number of bundles and ports per bundle. Join blocks also must have at least one input and one output port, and require that corresponding ports of each input bundle connect to output ports with the same dimensions and data type. The latter is necessary to insure that no matter which bundle receives data, the output bundle will always provide the same kind of data.

**Wraparound** blocks store data between passes through the algorithm, to implement adaptive parameters or tapped delays. They take **two** inputs -- a constant that reserves space for their data, and another input that provides the data. When a wraparound block executes during a frame, it passes its constant input on to its output. Once the fi-ame has finished, the data from the second input is transferred into the space held by the first. It will then be the data transferred to the wraparound block's output in the next fi-ame. To work properly, wraparound modules require that their first input be a constant, and that no other blocks read that constant directly.

Undefined blocks represent uncertain steps in **an** algorithm. They are useful in top down algorithm design. When the user knows what functionality is required at a certain point in **an** algorithm, but cannot find a suitable function in the library or is unwilling to search the library and lose his train of thought, he can use an undefined module **as** a place holder. Once the top level design is done, he can convert each undefined block into a function block, after locating the proper library function or defining a new one. Alternately, the user can delete **an** undefined block and replace it with **a** block diagram. Undefined blocks have a variable, user-controlled number of ports, so that all relevant connections can be made in the top level algorithm. Undefined blocks are not allowed in a completed program, because they have no associated definition, and cannot be simulated or translated into code.

# **C.** Representing control structures

The blocks in an RVMDES block diagram are connected into programs that are a hybrid between a data flow diagram and a flow chart. Like data flow diagrams, they explicitly show how individual variables flow through the steps of **an** algorithm, making the functionality of the algorithm more obvious. Unlike data flow diagrams, they must include some description of control flow, to allow the loops and conditional executions required in image processing algorithms. This means that the graphs must take on some of the character of a flow chart. To make data flow and control flow explicit in the same graph and ensure that it translates into a valid program, certain rules must be imposed on the struc-

ture of the graph. This section explains in more detail the advantages and limitations of the data flow diagram and flow chart, how a mixed representation can retain the benefits of each, and what rules must be imposed on that representation.

#### **1.** Data flow diagrams and flow charts

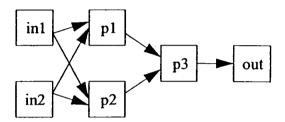

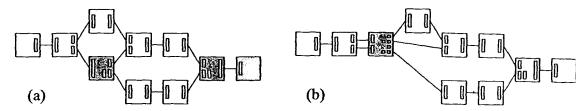

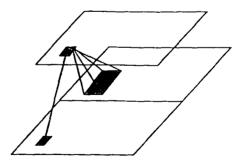

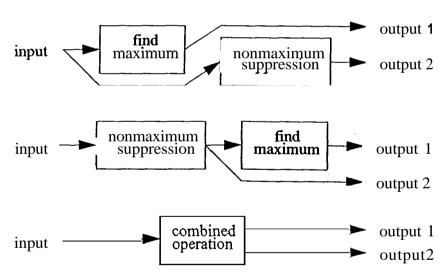

The data flow diagram, **as** depicted in figure 2.1, uses boxes to represent functions, connected to show how data flows between them. This allows a viewer to quickly see what operations are applied to what data, and thus to quickly understand the algorithm. While the representation does not provide an explicit execution order for its blocks, the order is tightly constrained, because each block executes once, after blocks that create its inputs and before blocks that use its outputs. Beyond that, the order is arbitrary. Thus, to convert a data flow representation to an executable, the blocks can be listed in arbitrary order, rearranged to fit the constraints, producing a valid execution order, then translated one at a time to into machine language, or a compilable programming language.

figure 2.1 - data flow diagram

This representation works when each block is used exactly once, but many computer vision applications do not have this simple linear structure. Often programs must iterate until some data dependent condition is satisfied, or must execute only one of a set of functions, again depending on the data. The data flow representation cannot handle these structures, because it cannot specify that **only** one of several output connections receive output data, to implement a conditional branch, and cannot specify that only one of several input arcs should be read, to close a loop. Further, the simple determination of execution order would not work, because the blocks no longer execute once each.

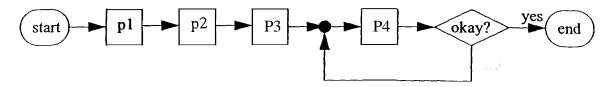

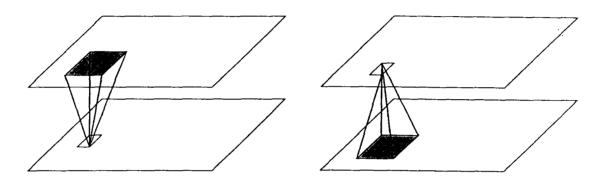

A second type of block diagram is the flow chart, shown in figure 2.2. In this representation, connections show order of execution of the blocks, not the data flow between them. This allows the inclusion of decision points, represented by diamonds, which can direct program execution along one of several paths. These paths can then be rejoined at nodes, represented by small circles, to implement the loops and parallel paths that computer vision algorithms require. Flow charts can be converted into programs written as code segments representing sequences of connected blocks, glued together by conditional branch statements representing the decision points. Unfortunately, the functionality of an algorithm represented by a flow chart can be difficult to understand, because while all of

the operators are shown graphically, there is no indication which data they operate on.

figure 2.2 - flow chart

#### 2. Mixed representation

The **RVMDES** block diagram representation is a compromise between the flow chart and data flow diagram, retaining the flow chart's ability to control which blocks are executed, but at the same time making data flow explicit. The compromise stems **from** two observations about how flow charts can be modified to be more like data flow diagrams without impairing **their** ability to implement control structures.

The first observation is that flow chart connections can be thought of as bundles of connections carrying all of an algorithm's active data. By making this replacement graphical, the diagram can show the existence of separate data items without affecting order of execution. Further, a flow chart's start and *end* blocks can be replaced with input, constant and output blocks to terminate the various connections, so that at least those variables will be identifiable. Again this does not hurt the flow chart, because the clusters of inputs and outputs still clearly represent start and end.

The second observation is that a sequence of processing blocks bounded by decision points (diamonds and circles) can be converted to a data flow diagram, reading its inputs from a bundle leaving **the** decision point preceding it and writing its outputs to a bundle entering the decision point ending it. Because the sequence contains no decision points, it can be reassembled from a data flow diagram by constructing **an** execution order **as** discussed earlier. When the sequence begins or ends with the clusters of input and output blocks, they can simply be added into the data flow diagram. The resulting graph is a set of data flow diagrams, connected by decision points.

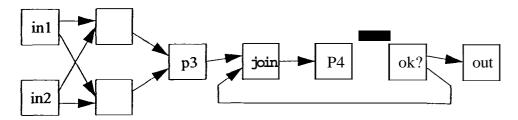

For consistency, the diamonds and circles are replaced with branch and join blocks, completing the transformation to an **RVMDES** block diagram. The **RVMDES** block diagram in figure 2.3 shows the advantages of this transformation. Unlike the equivalent flow chart in figure 2.2, the RVMDES block diagram shows the user what the first half of the algorithm is actually doing. And unlike the data flow diagram in figure 2.1, the RVMDES

block diagram is able to implement the second half of the algorithm.

figure 2.3 - R VMDES block diagram

The only problem with the representation is that it looks like a data flow diagram, but is not one. The blocks must be connected in such a way that the diagram can be converted back into a flow chart, with its explicit execution order. Thus additional rules must be imposed on block diagrams to insure that they are properly connected.

#### 3. Separate flows

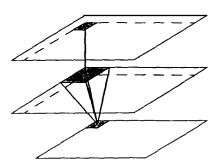

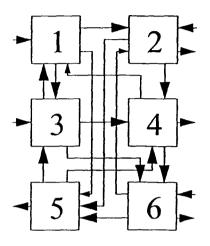

The first rule binding proper RVMDES block diagrams is that they must be divisible into flows, as in the block diagram in figure 2.4. Each flow consists of a set of blocks, containing no branches orjoins, reading all inputs From one output bundle of a branch orjoin block, and writing all outputs to one bundle of another branch orjoin block. Because each flow is actually a data flow diagram, an execution order can be constructed for each, as discussed earlier. The flows can then be glued together to form an executable program, using jumps and conditional jumps to represent join and branch blocks. In a properly constructed block diagram, RVMDES can even determine which blocks belong to which flow, by considering each input bundle of each branch and join module, following connections back to a single bundle, and recording any blocks visited along the way

figure 2.4: RVMDES block diagram, consisting of flows (shown as shaded rectangles), separated by branch and join blocks (dark blocks, with many ports)

Actually, it is even possible to extract flows **from** an improperly constructed diagram, like the one in figure 2.5a. The function block circumventing the branch block (shaded) obviously belongs with the **two** modules that depend on it. Thus, it could simply be grouped with those modules, and **an** execution order could still be constructed. On the other hand, it could also be moved to the **far** side of the branch module as in the equivalent block diagram in figure 2.5b. This breaks the diagram into logical sections, and makes it readily

apparent which modules belong to which sections, what data is being passed between sections, where **as** the user must work to parse figure 2.5a into sections. Because the entire point of the data flow diagram is to make a program quickly and easily understandable for the user, and because the rule requiring separation of flows helps insure this, it is enforced, even though RVMDES could write programs without it.

figure 2.5 - (a) invalid block diagram withfunction circumventing branch and (b) the valid version

#### 4. Input and output flows

The second rule binding RVMDES block diagrams is that among its flows, only one may contain input blocks, and only one may contain output blocks. In addition, the input flow may not read from branch or join bundles, nor may the output flow write to branch or join bundles. Again, this feature is not strictly necessary, but it facilitates code generation and program understanding.

In deriving the RVMDES block diagram, the starting point for a program was replaced with the set of all input modules. Working backwards, the code generator can determine which flow to execute first by locating the flow containing input modules. This restriction is somewhat limiting, because by spreading inputs throughout an algorithm, the implementation could read only the ones it needs, and only as they are needed. In a parallel processing implementation, this may allow a frame to begin earlier, before all inputs are ready. However, in a reconfigurable vision machine, each processor or piece of hardware is expected to read certain inputs at certain times. The only way to be sure that this happens is to read inputs as the first step of the algorithm.

The idea of **requiring** one output flow also follows **from** the derivation of the block diagram, but is not strictly necessary and is only implemented **to** help the user. If **an** algorithm had several output **flows**, each would have to have the same number of output

blocks, with the same set of data **types** and dimensions, to ensure that the hardware running the algorithm always output the same type of data. If the outputs have the same data

type and dimension, they could be funneled **through ajoin** module to produce one flow,

without much difficulty. This would enhance readability and allow RVMDES to easily

order output blocks to check for matching data type and dimensions and to ensure that corresponding blocks are sent in the proper order. Therefore, the RVMDES block diagram

specification requires such a reduction to one flow, even though it could write code without it.

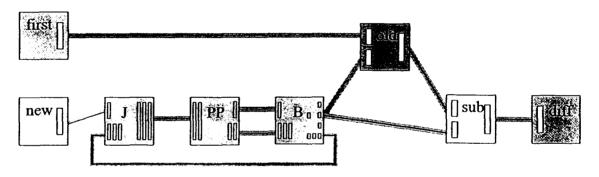

### D. Two example diagrams

Given the preceding explanation of the types of blocks and their connectivity, it is now possible to examine a few example diagrams, to see that they are easily interpreted. The first example is a motion differencing algorithm, shown in figure 2.6. **An** input block (yellow) reads an image at the beginning of each fiame. The image is then processed by **an** undefined function *PP*, embedded in a loop between branch and a join blocks (all grey). The loop repeats until the results of *PP* meet some condition, probably implementing some kind of smoothing or thinning. The output of this loop flows to a function module (white), where it is subtracted from the output of a wraparound block (dark grey). The wraparound serves as a delay, providing the loop output from the previous frame, or data fiom a constant block (green) during the first frame. Thus the, output of the function block is a difference image. This image feeds an output block (pink), which writes the image to a file or output device, ending the frame. A dotted line feeding the second input of the wraparound block reminds the reader that the data is read into the wraparound's buffer after the fiame has ended, and so does not affect the frame in which it was generated.

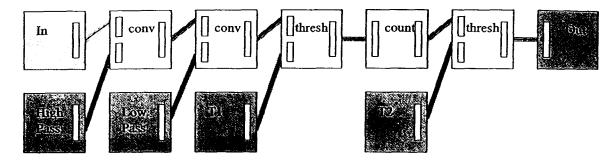

figure 2.6 - a block diagram

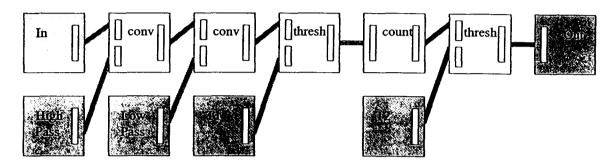

A more complex example, shown in figure 2.7, will be used to demonstrate the various capabilities of RVMDES throughout the thesis. Despite its complexity, the block diagram structure allows a user to quickly understand its function. As the algorithm begins, two constants are used to generate a **mask** for a convolution. The algorithm then thresholds its single input and finds the moment and a convolved version of the thresheld image. A branch block passes the convolved image and a mystery parameter to one of two parallel paths. The moment input to the branch is not passed through, so presumably it is used to decide which path to take, indicating that the program is intended to recognize two types of objects. In each path leading from the branch, the convolved image is processed by some function IA or IB, then passed through a join block to an output. Each path also sends a constant value through the join block to an output, showing which path was traversed. The mystery parameter sent through the branch block is incremented along either path, then output and sent to a wraparound block to be used in the next frame. Apparently, it will record the number of frames processed, plus the initial value in the constant labelled p0. From this short analysis, the user can determine that the algorithm distin-

guishes two kinds of objects, processes them differently, then outputs which type it found, the result of the processing, and the number of objects processed so far.

fig 2.7 - a larger block diagram

## E. Editing algorithms in RVMDES

RVMDES supports the easy-to-interpretblock diagram algorithm representation by providing an editor that facilitates building and modifying the diagrams. This section explains how the editor works. Specifically, it covers how the user manipulates blocks and connections to build a block diagram, and how he adjusts the special parameters associated with each block.

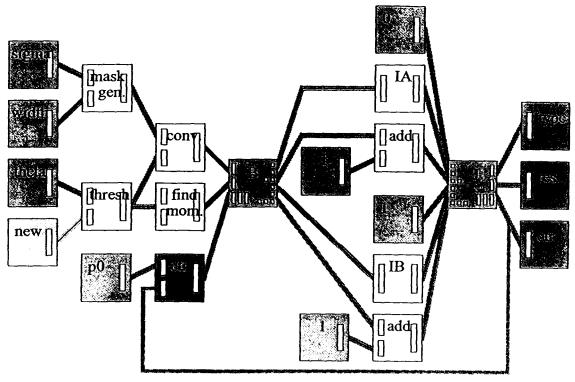

#### 1. Manipulating modules and connections

The editor, shown in figure 2.8, consists of a module generator (left) and an editor window (right). Buttons in the module generator (left) create instances of the 8 kinds of blocks, which can be dropped onto the editor window's canvas, moved around, and deleted when they are no longer needed. The various kinds of blocks are color coded as in the preceding examples, so the user can quickly search a program for a particular kind of block. In addition, the blocks are named so that the user can quickly see and recall what each is doing. Function blocks are associated with specific library functions, chosen fiom a dialog box that appears when the user creates a new function block. To make the choice easy, the dialog box hashes functions by categories such as thresholding and morphology, and allows the user to select a category, then a function fiom the limited list associated with

that category. These features make it easy to create and work with blocks.

Blocks are connected through their input and output ports, shown respectively along the left and right side of modules. Clicking on a port begins a new connection there, and clicking on a second port ends the connection. If the user clicks in the center of a block or creates a new block while a connection is in progress, RVMDES will try to finish the connection at that block. If the block only has one port, it will finish the connection at that port. Otherwise, it will pop up a list of ports and their associated parameters, allowing the user to choose the ending port by name.

figure 2.8: module generator and main software editor

Branch, join and undefined blocks have extra ports, as shown on the branch module in the bottom right comer of figure 2.8. The outer columns of ports represent inputs and outputs as with all blocks. The inner columns mark boundaries between bundles of ports, and also can be used to connect all ports in a bundle at once. This reduces work when entire bundles must be connected between branch and join blocks. The remaining two columns allow the user to create new ports. For a branch block, adding an input port adds a corresponding port to each output bundle, and adding an output actually adds a new bundle. Joins are exactly opposite. The ability to add extra ports from the block icon is provided because the need for an extra port is often not discovered as the user attempts to finish a connection at a branch or join block that has no free ports. Being able to add a new port at that time allows him to finish the connection, rather than aborting it and starting a new one.

Once connections are made, they are color coded according to the type of block that produces them and the data type of the data they represent. This helps the user follow one of a ribbon of parallel connections, and provides a quick way to check data types. The second input to a wraparound is even shown **as** a dotted connection to remind the user that it is not used during regular execution. To furtherenhance program readability, connections can be broken into segments, such **as** the dotted connection along the left of the editor in figure 2.8. This allows the connections to be routed around other modules and connec-

tions, so the entire connection is visible, and does not cross other connections.

#### 2. Specification windows

To provide information beyond the existence of blocks and connections between them, RVMDES provides a specification window associated with each block. From this window, users can set parameters, add and delete ports and view or create function definitions.

The principal purpose of specification windows is to let the user set the special parameters associated with each block. For instance, the user can change a block's name from its default (the function name for a function block, and null for any other blocks) to something mnemonic. Also, he can change the data type of any of the block's output ports, specify the flavor and define the data of a constant block, or set the names of files that input, output and initializing constant blocks use during simulation. Finally, he can set the dimensions of input and constant blocks. The dimensions of other types of blocks are not considered parameters. Instead, they are set automatically based on the dimensions of the blocks fi-om which they read, to save the user time and prevent him from inserting errors into the program.

The second purpose of the specification window is to provide an interface for the user to view and change a block's ports. For most modules, this means viewing the mapping between port names and numbers prior to deciding which port should begin a connection, or adding special output ports to write the dimensions of any original output port. The latter can be useful when an output is a list whose length is not known until the list is created, but is needed for a later function. In addition, the user can create special input ports for input or constant blocks, to read dimensions from another block's dimension output ports, rather than having them set in the specification window. This allows two input or constant blocks to match dimensions even if the dimensions are unknown, such as when defining a new function with two inputs. One more set of ports that the user can change are those belonging to branch, join and undefined blocks. Each of these blocks has a variable number of input and output ports, and the user can add, reorder and delete both them, as necessary to attach, remove or untangle connections that must go to or through the block.

A final pair of tasks which can be accomplished **from** specification windows is viewing the function definitions associated with function blocks and converting undefined blocks into function blocks. Functions can be primitives (defined by C code, which RVMDES uses to translate the algorithm into **an** executable) or macros (block diagrams composed of primitives and other macros), and both types can be viewed by calling a definition window **from** a h c t i o n module's specification window. Viewing a primitive definition will invoke a code editor to show the various parts of the definition. Viewing a macro definition will invoke a software editor to show the macro's block diagram. If a function is a macro, its specification window will also contain a button to expand the block, replacing it with its block diagram in the software editor containing the macro. Like function blocks, undefined blocks may be defined **as** primitives or macros. However, the user must provide these definitions. Buttons in **an** undefined block's specification window allow the user to invoke **a** code editor or a block diagram editor, and when the user saves the defini-

tion, the undefined block will be replaced with a function block representing that definition.

#### F. Simulation

Once the user builds an algorithm, he will generally simulate it to see whether it generates the desired results, and to track down problems and modify the algorithm when it does not. He will then iteratively modify and simulate the algorithm until it performs correctly. To make this iteration as painless as possible, the RVMDES algorithm simulator is embedded in the block diagram editor, allowing the user to simulate using the block diagram itself as the interface. The simulator does not require an algorithm to be compiled, so the user can simulate parts of an algorithm while others are still under construction and contain "errors", such as undefined modules. This section explains how the embedded simulator interface and the simulator itself work.

#### 1. The simulator interface

RVMDES's embedded simulator provides an interface much like a debugger for a standard programming language, where the user steps through lines of source code, executing them and viewing the data they produce. However, the RVMDES simulator differs from source code debuggers in three respects, deriving advantages from each.

First, the user clicks on blocks and connections, not text statements. Clicking through blocks allows him to **think** in terms of data flow, not in terms of C code implementation. The connections show him quickly which functions use which data, so he need not search for instances of a variable name in source code. The block diagram also hides the code that repeats the algorithm on each new frame, reducing the complexity of the program a little. If the user needs to simulate several consecutive frames to see whether wraparound blocks work, he can use the next-frame command, which switches the inputs to wraparounds, and attempts to update file names for input and output blocks so they can read and write sequences of data files. If the user wants to change the values of initializing constants between frames, he can manually change the file name from which the data is read.

A second difference in **RVMDES**'s simulator is that the order of execution of the blocks in the block diagram might not be fixed. It is constrained because a block may only execute when it has valid data on all input connections, but this oftenprovides multiple executable blocks at any given time. To guide the user through the simulation, RVMDES determines which blocks can be executed at any given time, and highlights them so the user knows which he can execute. RVMDES also tracks which connections hold data that has been written but not read, and highlights them so that the user knows which connections are worth viewing. Data on unhighlighted connections can still be viewed, but may be invalid if looping in the algorithm has caused upstream blocks to be reexecuted, and the changes have not propagated to the unhighlighted connection.

The third difference in RVMDES's simulator is that it does not require algorithms to be compiled before simulation. It uses compiled executables to simulate function blocks, but

this is transparent to the user, who steps through the uncompiled, high level algorithm. Because the algorithm is interpreted, the user can change it without leaving the simulation. If a block produces bad results, he can delete it, replace it with a new block, and continue simulation with it. Data that does not depend on the replaced block will remain valid, so unless the block is part of a loop, the user can repeatedly replace a module and simulate it until a desired output is produced. He can even build an entire algorithm this way, adding and testing one block at a time.

#### 2. How the simulator simulates

How **RVMDES** simulates a given block depends the type of that block. **An** input or constant block reads data fi-om a file or memory, and makes it available on its output port, and any connections beginning at its output port. **A** function block invokes an executable associated with the particular function it represents, reading data from the module's input connections, and storing results on its output connections. Branch blocks perform their series of tests, and pass data fi-om their input bundle to the first output bundle to pass its test. Join blocks similarly pass data fi-om a single activated input bundle to their single output bundle, while wraparounds just pass their first input on to their output. Undefined blocks cannot be simulated, because they are simply place holders. Attempting to simulate them will return an error message.

#### 3. Error Handling

While it is wise to remove errors such as invalid connections from an algorithm before simulating it, sometimes it is helpful to simulate a program that is still under construction. This is the case in top down design, where an algorithm is built from undefined blocks, which RVMDES considers syntax errors, arid the user would like to simulate each block as it is defined, even though other blocks remain undefined. Thus, while RVMDES provides an error checker to locate errors in an algorithm, it does not require the user to run the checker prior to simulating an algorithm. This is not a problem, because the simulator interprets the algorithm and does not require a particular piece to be syntactically correct until it attempts to simulate that piece.

To allow simulation of algorithms with possible errors, RVMDES checks each block before simulating it. If the block violates any of the simple syntax rules constraining RVMDES block diagrams, the simulator complains and refuses to simulate the block. Further, RVMDES completely ignores the more subtle errors involving conditional execution. This is because they exist only to help **RVMDES** determine an execution order and to make the code readable. During simulation, the user determines the execution order, and any code readability is not critical at every phase of algorithm construction. Readability will be ensured by the automatic error check prior to generating the **RVM**.

# G. Summary

RVMDES provides a block diagram representation for computer vision algorithms that makes the exact function of an algorithm very explicit, without sacrificing the ability to implement necessary control structures such as data dependent loops. RVMDES also provides a software editor, from which a user can quickly and easily build block diagram

algorithms, then iteratively simulate and modify them until they produce the desired results. The time spent in this iteration is minimized by allowing the user to simulate algorithms at the block level, to iteratively edit and simulate single blocks, and to simulate pieces of a program that is still under construction. A library of computer vision functions provides predefined blocks, so that the user can think entirely in terms of algorithm building blocks, not the code to implement them. These features ensure that most of the time a user spends in the software phase of the RVM design cycle is spent evaluating algorithms, not writing and debugging code or running simulations. All of this is made possible because a block diagram can completely describe the limited set of functionality needed to implement image processing programs.

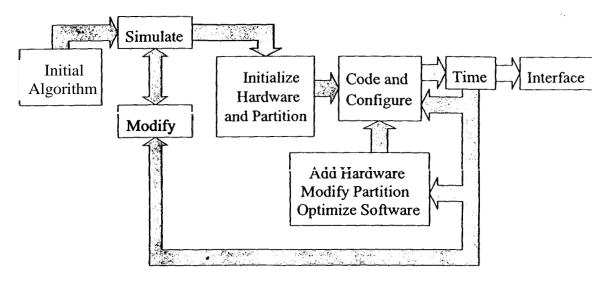

# III. Streamlined Hardware Design Cycle

Once the user has designed an error **free** RVM algorithm, he must design the hardware to implement it. The hardware design cycle follows the same steps as software design: creating an initial design, then repeatedly testing it and modifying it until it provides the desired results, Creating an initial hardware design for an RVS means choosing a set of hardware modules, choosing which parts of the algorithm will run on each module, configuring motherboards to hold the modules, and generating code for any processor modules. Testing the design involves simulating the processing on hardware modules and interactions between them, determining whether the whole system runs fast enough to meet design specifications, and if not, determining why not. Modifying the design means changing the software, hardware, or partitioning of software onto hardware, to eliminate processing bottlenecks.

The design cycle may involve many iterations of testing and modifying, because the choice of modifications involves trial and error, and because only small amounts of hardware are added every iteration. The latter ensures that each bottleneck is remedied with a minimum amount of hardware, thereby keeping costs down. To speed the user through the design cycle despite the large number of iterations, RVMDES provides tools that make each step efficient, by taking advantage of two things: the fact that image processing applications require on a limited set of hardware, and the highly structured block diagram representation developed for the software editor. By limiting itself to the set of image processing hardware modules in the Egipt RVS, RVMDES can include enough information to simulate each type of hardware and the interactions between them, so that it can automatically estimate timing for the entire system. In addition, the RVS provides a standard module interface and set of motherboards, so transforming a network of hardware into a final hardware design reduces to a bin packing problem, which can be automated. While the actual choice of hardware and partitioning cannot be automated, RVMDES's block diagram representation for software provides a simple interface from which to quickly perform those steps. This chapter explains how exactly RVMDES leverages its RVS and block diagram representation to make each step in the design cycle as fast as possible.

# A. Creating an initial design

The initial step of hardware design is to guess what hardware will be needed to run an algorithm in the time required by the RVM design specification. RVMDES chooses the minimum amount necessary to run the algorithm. While it is unlikely that this minimal hardware will run fast enough, it has two advantages. First, it does not waste expensive hardware remedying imagined processing bottlenecks. Instead, the user is forced to examine the system timing and see the actual bottlenecks before committing any hardware to fix them. Secund, the minimum hardware set can be generated semi-automatically, saving the user time and effort.

Once the hardware set is chosen, it must be converted into a hardware design, by partitioning software onto the hardware modules, generating code for any processor modules, and configuring the modules onto motherboards. Again, these steps can all be done semiauto-

matically, saving the user time and effort. This section explains how RVMDES performs these steps, in particular how it chooses the minimum hardware set and partition, how the user must help, and how RVMDES off-loads most of the work of configuring mother-boards from the user.

#### 1. Minimum hardware set and partition

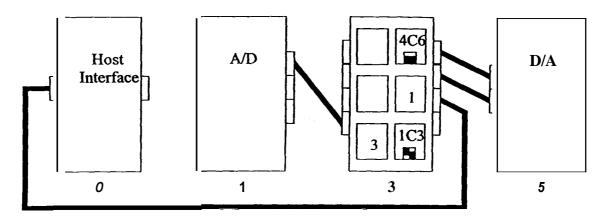

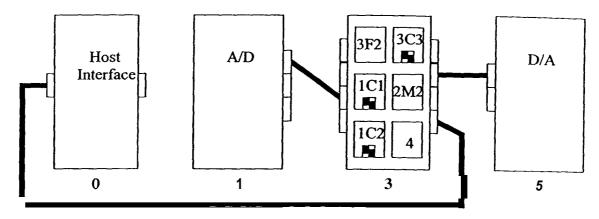

A minimum hardware configuration for an Egipt RVM has four parts: interface, processing, input and output. The interface consists of a single host interface module, which must be present in any Egipt RVM, so that the RVM can communicate with its operator. The processing part of a minimal configuration is generally a single C44 processor module. All software blocks except inputs and outputs are partitioned onto this processor, so that when timing is generated for the system, it will be timing for the algorithm, uncluttered by delays from passing data between hardware. There are only two cases where a single C44 is not the processing element: when the algorithm contains only inputs and outputs, so processing is unneeded, and when the algorithm cannot fit into the C44's memory. In the latter case, the user must generate an initial system by himself, using the steps outlined later for modifying a hardware set. The input part of an RVM is performed by one or more A/D modules, of the only variety currently in the Egipt RVS. Each provides 3 interchangeable input channels, so one module is provided for every three input blocks in the algorithm.

The output part of an RVM cannot be generated automatically, since more than one type of hardware module is capable of disposing of output data. Thus, the user must provide a mapping between output blocks and their host hardware, **as** explained in the next section. If in the future there are multiple types of interface, processor or input modules, each type will be assigned using the same type of interface currently used to match outputs to hardware. This will involve more work for the user, but should still be better than assembling hardware fiom scratch.

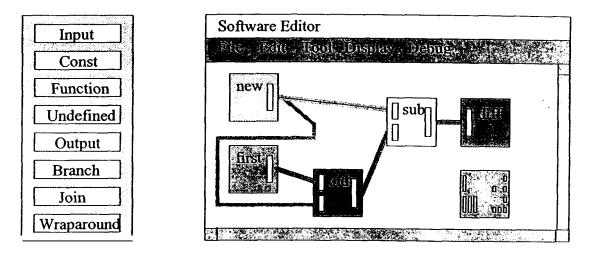

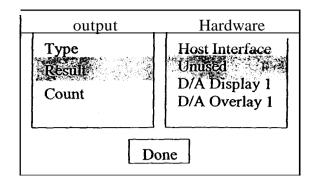

#### 2. Choosing output hardware

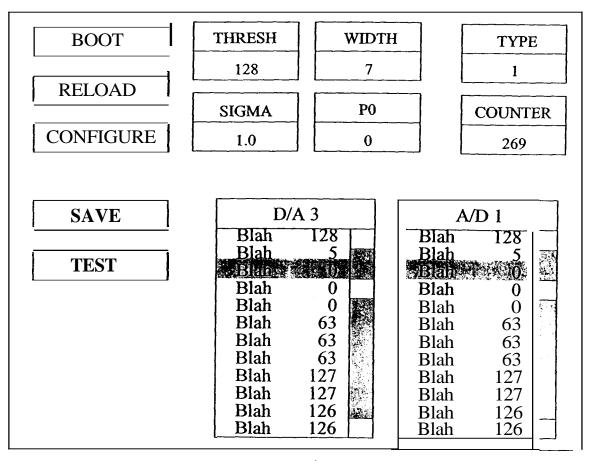

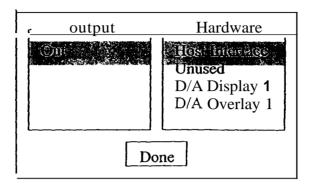

**An** algorithm output block can be assigned to a D/A module's image or overlay channels for display, or to the host interface module **as** a statistic, or it can remain unused on the hardware that creates it. In the future, there will likely be additional output devices that can host an output block. It is not possible to specify which hardware **an** output should use until the hardware is generated, so **RVMDES** asks the user for this mapping **as** it generates hardware. RVMDES provides a window, as in figure 3.1, listing the names of output blocks and the hardware that can host them. If a module has multiple channels, like the D/A module in the example, the channels are shown separately. Selectable entries in the two lists identify the output under consideration, and the hardware it is currently assigned to.

figure 3.1 - The output mapping wizard

#### 3. Finishing a hardware design

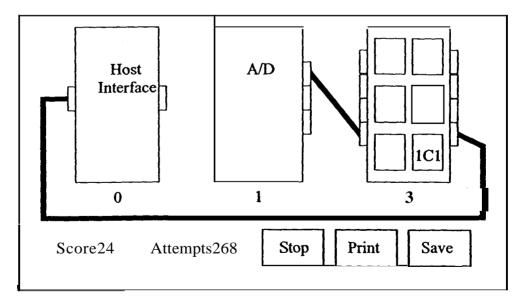

When **RVMDES** creates an initial hardware design or the user modifies the algorithm, hardware or partition, the user must command RVMDES to finish the RVM design. RVMDES will then generate executables for any processors, and determine how to configure hardware modules onto motherboards so that all required intermodule connections are made, with a minimum number of cables and overlays. It will display the configuration diagram for the user, who must assemble matching RVS hardware.

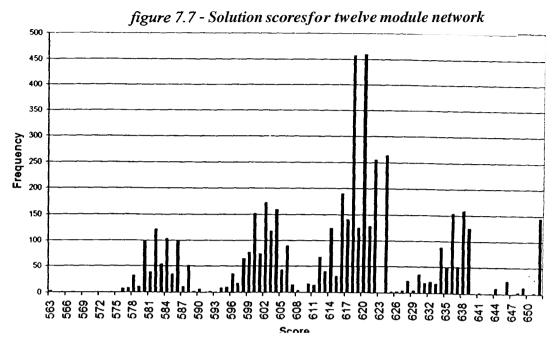

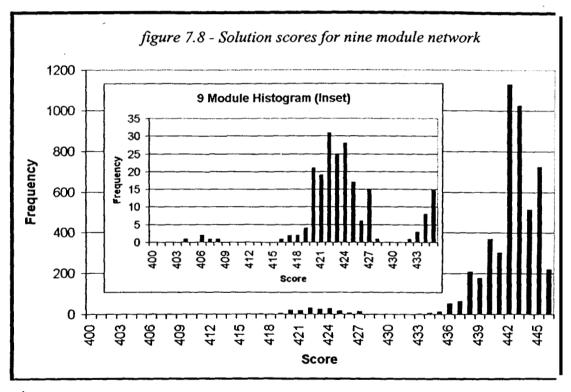

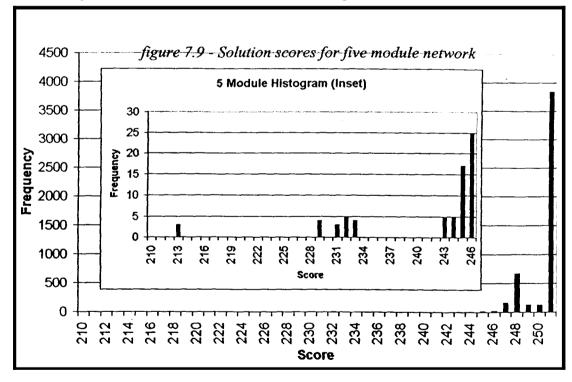

Unfortunately, RVMDES cannot always find the optimal configuration. The space of possible configurations can be huge, especially **as** the number of hardware modules grows, and it is not possible to search much of that space before the user becomes impatient. Therefore, RVMDES does not expect to search the whole space. **As** it searches, it displays the best valid configuration it has found so far, and allows the user to stop the search any time after finding the first one. The user can then decide whether his time or the possibility of a more efficient design is more valuable.

To help the user decide when to stop searching, RVMDES augments its configuration diagram with a score for the current, best configuration, and the number of suboptimal configurations found since the current best configuration was discovered. As the number of suboptimal solutions grows, the user should have increasing confidence in the current best solution, and feel comfortable stopping the search. Once the user does stop the search, the configuration diagram will remain, so the user can return later to search for a better configuration.

#### 4. Summary

RVMDES automates the drudgery of the initial hardware design and partitioning. It can do this because the limited scope of image processing functions allows a block diagram software representation and a limited set of RVS hardware. The block diagram allows RVMDES to easily recognize an algorithm's input, processing and output needs, and the limited set of hardware allows it to propose hardware to meet those needs. It can then automatically generate the required hardware, or let the user choose between viable alternatives, rather than making him choose hardware and a partition from scratch. Further, by restricting the hardware set and providing a common interface for each module and moth-

erboards to connect the modules, the Egipt RVS reduces hardware configuration to a search problem, which RVMDES can mostly automate. The only part the user must play in finding the configuration is to determine when to stop searching.

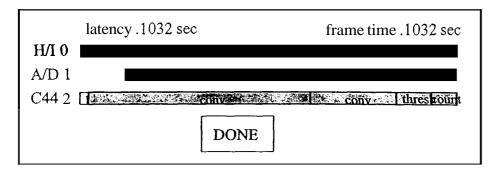

### **B.** Estimating Timing

The second step in the hardware design cycle is to simulate each hardware element running its piece of the algorithm and interacting with other hardware. From the results of **this** simulation, the user must determine whether the frame rate and latency for the entire system meet design specifications, and if not, how to change the hardware or software to reduce the difference. Because **RVMDES** will design with a limited set of hardware, it can incorporate enough information to simulate each type and model the interactions between them, to give the user an accurate picture of the entire system's timing.

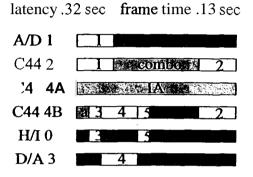

Unfortunately, writing and using accurate simulators is a time consuming prospect. **As** evidence, the Texas Instruments **C40** emulator does not even attempt to model timing, and the simulator for the Philip's Trimedia DSP runs two thousand times slower (according to Philips) than the actual chip. In the absence of a viable simulator for the Egipt RVS's single processing module, the **C44**, RVMDES determines RVM timing by estimation. That is, it estimates the time required for each operation on each hardware module, then schedules the operations onto the modules, inserting delays to account for interactions between hardware modules. This section explains how RVMDES estimates timing for various operations, how it schedules the operations to find total system timing, and how valid the timing estimation is.

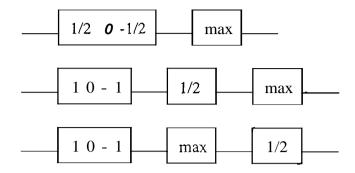

#### 1. Timing operations on processors

RVMDES estimates the time required to run software blocks by using formulae associated with each block. **This** is possible because of two restrictions on the software representation: **RVMDES's** available function blocks are all defined in its code library; and RVMDES always uses the same compiler to turn those functions into executable code. By compiling and testing **a** function as it is added to the library, it is possible to see what factors affect the time of the resulting executable, and to turn this knowledge into one or more formulae which can be stored with the function's definition. If the **RVS** included multiple kinds of processors, **a** function could be compiled and tested for each chip, providing additional formulae. When a function is used in **a** program, **RVMDES** determines which formula to apply, based on conditions in the program, then applies the formula to estimate timing. **This** section explains what factors are involved in such a formula, and what factors require multiple formulae or modifications to formulae.

The basic formula for software timing is AXY + BY + C, where X and Y are the dimensions of an image read or written by the function, and A, B and C are experimentally determined coefficients. The formula reflects the fact that most software blocks are implemented as nested loops over the rows and columns of an image. Time is spent in the loop kernel (A), resetting counters for each row (B), and setting up for and cleaning up behind the function (C). This basic formula has three variations, for functions with data dependencies, secondary inputs, or inputs with reduced dimensions. The first variation adds terms to the

formula to compensate for dependence on the value of certain scalar, integer inputs. As an example, the hction to generate a Hamming window builds an image of a disk with area proportional to an input T. Pixel values inside the disk take longer to calculate than those outside, but the additional time per pixel is fixed, and the number of pixels inside the disk is proportional to T. The formula AXY + BY + C + DT reflects this. The second variation adds terms to a formula to compensate for secondary input images. This is necessary for windowing operations, which have their main loop over an image, and an internal loop over a window. The main loop kernel, which executes once per pixel in the main image. must spend time processing each window pixel, preparing for each window row, and preparing to apply the window. Thus, for a function using an M by N window, the timing formula expands to AXY + BY + C + DXYN + EXYMN. This formula can be reduced somewhat by deleting the fourth term (for resetting window row counters) if RVMDES unrolls the internal loop. The third formula variation occurs when a function that is designed to process an image actually reads an array or scalar instead. RVMDES reduces the looping to compensate, at which point timing follows the formulae AY+C for an array, or C for a scalar. The per-pixel and per-function coefficients may or may not be the same across these reduced formulas, so in some cases the coefficients for each reduced dimension variation must be recorded.